最近将多年来收集到的教学视频、国内外图书、源码等整理整合拿出来, 涉及arm、Linux、python、信号完整性、FPGA、DSP、算法、 stm32、单片机、制图、电子模块、kali、出版社图书等。大小约1.5TB+。 详情: https://www.bilibili.com/read/cv20701606

今天为数字钟写display显示代码,还是要用到testbench和modelsim,上次的方法感觉好乱好乱的,今天在前面学习的基础上又查找资料,学到了新的方法,有了新的体会,在这里记录下来。有部分图片啥的是从前面的文档里复制的,更新的主要是今天学习的操作方法。

注意,从今天开始,testbench使用VHDL语句了!

假设现在已经写好了一个电路vhdl,编译也没问题了,什么都没问题了,就差仿真了。

- 设置testbench语言

这里使用VHDL语言,确认。

- 生成testbench

点击之后,quartus会自动生成以.vht为扩展名的testbench文件。

- 建立modelsim工程

打开modelsim 10.1c

打开后是没有work库的

所以要新建work库

取名为work

在建立的library库之后,要再建立一个工程project

我们为这工程取名为display

点击OK后会弹出另一个对话框

因为我们的VHDL元件文件和testbench都是使用quartusII来生成的,所以我们直接选择“Add existing file”将我们设计的display元件和testbench都添加进来,为什么这两个文件都要添加呢?

因为仔细看testbench中,他有个component,他其实就是引用了display元件,要不他知道要对输入引脚的信号进行什么操作呢,对吧。

添加display元件

确定之后,我们会看到工程中会添加了display.vhd元件文件

接着我们在添加testbench文件就行了

是simulation->modelsim中的display.vht

最后整个工程中包含了两个文件,一个.vhd一个.vht

这样一个工程就完成了。

- testbench文件编写

在把整个大环境搭建完成后,我们就要修改quartusII直接生成的testbench文件,在上面工程的.vht文件上右键选择edit

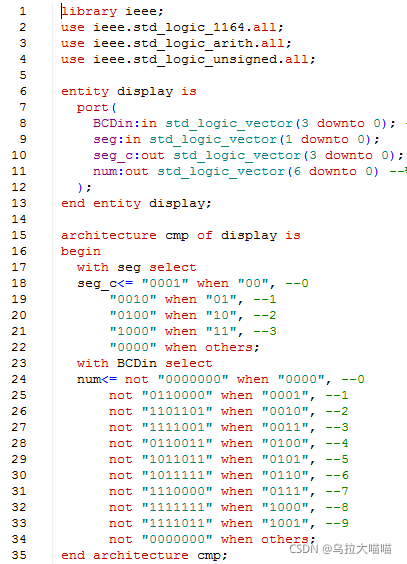

在编辑界面可以对testbench进行修改,下面先把vhdl的元件代码复制到这里,让大家看看这个元件是什么,才能测试,对吧,所以先看元件是干啥的

这个用来驱动4位7段数码管,seg用来控制选第几个数码管,00表示第一个,01是第二个,10是第三个,11是第四个。BCDin是按BCD码的输入数字,将BCDin转成int型就是对应的数字。输出的seg_c是直接连到硬件的位选,num连到段选。

那么他的testbench怎么写的呢?

LIBRARY ieee; USE ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; ENTITY display_vhd_tst IS END display_vhd_tst; ARCHITECTURE display_arch OF display_vhd_tst IS -- constants -- signals SIGNAL BCDin : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL num : STD_LOGIC_VECTOR(6 DOWNTO 0); SIGNAL seg : STD_LOGIC_VECTOR(1 DOWNTO 0); SIGNAL seg_c : STD_LOGIC_VECTOR(3 DOWNTO 0); COMPONENT display PORT ( BCDin : IN STD_LOGIC_VECTOR(3 DOWNTO 0); num : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); seg : IN STD_LOGIC_VECTOR(1 DOWNTO 0); seg_c : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COMPONENT; BEGIN i1 : display PORT MAP ( -- list connections between master ports and signals BCDin => BCDin, num => num, seg => seg, seg_c => seg_c ); init : PROCESS -- variable declarations variable BCDintemp:std_logic_vector(3 downto 0); BEGIN -- code that executes only once BCDin<="1111"; seg<="11"; wait for 500ns; BCDintemp:="0000"; for i in 0 to 9 loop seg<="00"; --out 0001 BCDintemp:=BCDintemp+'1'; --use "+" must include std_logic_unsigned library BCDin<=BCDintemp; wait for 500ns; end loop; WAIT; END PROCESS init; always : PROCESS -- optional sensitivity list -- ( ) -- variable declarations BEGIN -- code executes for every event on sensitivity list WAIT; END PROCESS always; END display_arch;

量BCDintemp来累加,看整个输出对不对。

- 编译

保存testbench,点击编译all

编译完成后会发现工程中的?号变为了对号√

说明编译通过了。

- 仿真

在弹出的对话框中选择仿真程序

点击OK后应该有一个object界面,如果没有,从view中选出来

在object界面中将所有的管脚都加到波形中:

在波形界面,修改为10ms,之后点击run就行了